Co-funded by the Erasmus+ Programme of the European Union

## Federation of remote labs, the PILAR approach

#### Platform Integration of Laboratories based on the Architecture of visiR – PILAR

2016-1-ES01-KA203-025327 Erasmus+ - Strategic Partnerships for Higher Education

Speaker André Fidalgo ISEP/IPP

- 1 VISIR System

- 2 VISIR Institutions

- 3 System Usage

- 4 Pilar Approach

- **5 Development**

#### 1. VISIR System

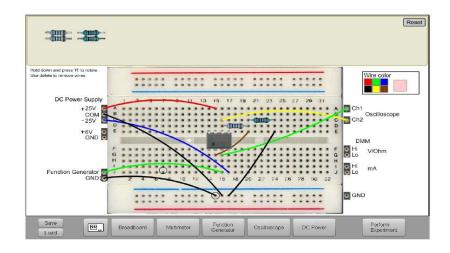

- Open Remote Laboratory

- Directed to Electrical and Electronics Experiments

- Developed at BTH (Blekinge Institute of Technology)

- Launched in 2006

#### 1. VISIR System

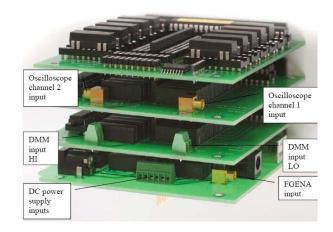

- Uses PXI instrumentation by National Instruments

- Function generator

- Oscilloscope

- Digital multimeter

- Triple output power supply

- Switching Matrix

- Componente Boards

- Instrument Boards

- Realistic Interface

### **2. VISIR Intitutions**

- Institutions within PILAR

- BTH (since 2006)

- UNED (since 2008)

- CUAS (since 2008)

- U Deusto (since 2009)

- IPP (since 2010)

- Institutions outside PILAR

- PUC-Rio (since 2016)

- FW Wien, UFSC, IFSC, UNR, UNSE, Georgia, India

• Number of Users

| Partner  | Users         | Teachers     | Institutions |

|----------|---------------|--------------|--------------|

| втн      | less than 100 | less than 10 | less than 5  |

| UNED     | 1000 or more  | less than 10 | less than 5  |

| CUAS     | less than 100 | less than 10 | less than 5  |

| UDeusto  | 1000 or more  | less than 10 | 20 or more   |

| ISEP/IPP | 1000 or more  | 10 - 49      | 5 to 9       |

#### **2. VISIR Institutions**

• Localization, i.e. Languages

| Partner  | EN | SV | ES | РТ | DE | PL | NL | AR | Other          |

|----------|----|----|----|----|----|----|----|----|----------------|

| BTH      | х  | х  |    | х  |    |    | х  |    | EL<br>More     |

| UNED     | х  |    | х  | х  | Х  |    | х  |    |                |

| CUAS     | x  |    |    |    | х  |    |    |    |                |

| UDeusto  | x  |    | x  | х  | х  | х  | х  | х  | RO, SL, CZ, RU |

| ISEP/IPP | х  | х  | х  | х  |    | х  | х  | х  | EL, KU         |

Login Methodology

| Partner  | Original | LDAP | Other | Guest Login |

|----------|----------|------|-------|-------------|

| BTH      | 1        | 1    | No    | Yes         |

| UNED     | 0        | 0    | JSON  | No          |

| CUAS     | 0        | 0    | GOLAB | Yes         |

| UDeusto  | 0        | 2    | No    | Yes         |

| ISEP/IPP | 2        | 1    | No    | Yes         |

• Electrical Experiments

| Partner  | Active<br>Filters | Passive<br>FIlters | Ohm and<br>KCL (DC) | Ohm and<br>KCL (AC) |

|----------|-------------------|--------------------|---------------------|---------------------|

| BTH      | Active            | Active             | Active              | Active              |

| UNED     | Active            | Active             | Active              | Active              |

| CUAS     | Past              | Never              | Active              | Past                |

| UDeusto  | Never             | Active             | Active              | Active              |

| ISEP/IPP | Past              | Active             | Active              | Past                |

• Electronics Experiments

| Partner  | Diodes | Transistors | Ampops | Logic  |

|----------|--------|-------------|--------|--------|

| BTH      | Active | Active      | Active | Past   |

| UNED     | Active | Active      | Active | Active |

| CUAS     | Active | Past        | Past   | Past   |

| UDeusto  | Active | Active      | Active | Never  |

| ISEP/IPP | Active | Active      | Active | Never  |

- Other Experiments

- Thevenin (Black Box)

- RL time constant

- Zener

- RLC

- DC-DC converters

- Temperature Dependency

- Power Dissipation

#### 4. PILAR Approach – What is it?

- Platform Integration of Laboratories based on the Architecture of visiR – PILAR

- ERASMUS+ European Project

- KA2 Cooperation for Innovation and the Exchange of Good Practices - Strategic Partnerships for higher education

#### 4. PILAR Approach – What is it?

#### **Partners:**

Universidad Nacional de Educacion a Distancia (UNED) Blekinge Tekniska Hogskola (BTH) International Association of Online Engineering (IAOE) Universidad de la Iglesia de Deusto Instituto Politecnico do Porto (IPP) Espoon Seudun Koulutuskuntayhtyma OMNIA EVM project management experts sl Fachhochschule Karnten-Gemeinnutzi (CUAS)

#### 4. PILAR Approach – Who Needs it?

- Many different stakeholders, including:

- high schools

- universities

- other education institutions

that need to increase their competences in electronics through real remote electronics experiments covering from simple to sophisticated experiments

- Specifically students and teachers of these institutions that need to increase their practical competences without the problems associated with the maintenance and physical restrictions of real electronics laboratories.

- Curricular development, interinstitutional co-operation, virtual mobility of students and academic staff, and integrated programmes of study, training and research.

#### 4. PILAR Approach - Main Activities

- Building an integrated platform of all the remote VISIR implementations in CUAS, UNED, IPP, UDEUSTO and BTH, that will be accessed as a federation of remote labs

- Building of a set of remote VISIR electric and electronics practices, at different complexities, served as Internet services

- Creation of a set of formal documentation for entering PILAR for use of teachers and universities and schools managements

- Use of all these services in the partners institutions

- Offering to other institutions at local, regional, national and European levels.

A1

#### 4. PILAR Approach - Advantages

- Larger set of practices

- More efficient and effective use of the VISIR resources

- Support for each of the remote lab services offered

- Innovative practical part of subjects

- Better control of the students' learning process

**Diapositiva 16**

A1

A much larger set of practices, oriented to different and tuned needs, for students in different academic levels at the school and at the university 2- A much more efficient and effective use of the VISIR resources of each of the partners, thanks to the transparent work-balance of users and experiments provided by the federation. The federation of remote labs also will make simple to add new experiments to PILAR becoming it in an easily scalable and maintanable platform

3- A service level agreement (SLA) type for each of the remote lab services offered

4- A much more innovative practical part of subjects related with electronics at high school and grade and master university levels, more flexible and reliable environment, specially taking into account the troubles faced by many students related with the need of moving to where the laboratories are.

5- A much better control of the students' learning process when they carry out real practices on electrical and electronics experiments through the remote laboratories provided by PILAR.

Andre; 07/11/2017

#### 4. PILAR Approach - Characteristics

- 1. Scalability.

- The VISIR system supports around 50 users at the same time

- Circuits can be replicated in different VISIR nodes

- 2. Reliability and availability.

- Redundancy

- Transparency

- 3. Set of experiments.

- VISIR is a REAL remote lab

- User will access the total set of experiments of all the VISIR nodes.

- 4. Tracking system.

- How many users are accessing each VISIR node

- Balancing and priorities

#### 4. PILAR Approach - Evaluation Points

- Number of available and federated VISIR platforms in PILAR

- Number of accessible experiments through PILAR

- Number of training courses offered in PILAR for different educational levels

- Number of students involved in training courses

- Number of institutions out of PILAR consortium that will access VISIR

- Number of institutions from countries out of the PILAR consortium scope

- Number of subjects in which PILAR outcomes will be used in regular courses

- Opinions and considerations gathered from surveys

- Support materials and documentation adequacy

#### **5. Development – Ongoing Steps**

- Technical Specs for Federation

- Cross User Policies

- Federation Policies on Availability

- System Data Sharing

- Experiment Listing

- Experiment Pedagogical Documentation

#### **5. Development – Guide Examples**

VISIR

|                                          | R         | toteiro da Experiência                                                                                                                                                                                                                                             |

|------------------------------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Paralelos Resistêr                       | icias (Ω) | <ul> <li>Observe os valores das resistências ao posicionar o mouse por cima, e confirme utilizando o multímetro<br/>digital;</li> </ul>                                                                                                                            |

| Paralelo AB 2k2 1<br>Paralelo BC 100k 10 | k 470     | <ul> <li>A imagem ao lado representa o circuito completo. Teste os diferentes tipos de associações possíveis e<br/>confira o valor da resistência equivalente em cada situação, utilizando o multímetro digital;</li> </ul>                                        |

|                                          | Dok<br>W  | <ul> <li>Experimente criar associações em série, em paralelas e mistas com diferentes valores de resistências, e<br/>confira com os resultados esperados da solução.</li> </ul>                                                                                    |

|                                          |           | <ul> <li>ATENÇÃO: Ao montar o circuito, sempre respeite a imagem e a tabela ao lado que indica quais resistências<br/>podem ser ligadas em paralelo. As resistências em paralelo na imagem podem ser ligadas em série, desde<br/>que sejam apenas duas.</li> </ul> |

| 470 2                                    | 20k       | <ul> <li>Exemplo: Pode-se ligar as resistências 2k2 e 1k em paralelo, e em série com a de 100k. Não será possível<br/>ligar a resistência de 1k em paralelo com a de 100k, neste caso, o sistema anunciará um erro.</li> </ul>                                     |

#### Confira a solução dessa experiência aqui

#### **5. Development – Teacher Interface**

| sua Max List (se possível) e implementará no sistema do VISIR. |                        |                    |           |

|----------------------------------------------------------------|------------------------|--------------------|-----------|

| Formulário                                                     |                        | Search:            |           |

|                                                                | ID                     | Valor              | Nó        |

| Nome:                                                          | Condensador            | 1uF                | E         |

| E-mail:                                                        | Diodo                  | 1N4148             | H         |

|                                                                | Diodo                  | 1N4148             | E         |

| Imagem do Circuito:                                            | F. Gen                 |                    | A         |

| Escolher arquivo Nenhum arquivo selecionado                    | Fonte CC               | +6                 | A         |

| Descrição do Circuito:                                         | Fonte CC               | +25                | F         |

|                                                                | Fonte CC               | -25                | В         |

|                                                                | Indutor                | 680uH              | G         |

|                                                                | OP_4_7:4_13:4_14:4_4:4 | _6 NC1 G C B NC2 H | H F NC3 u |

| 🖌 Enviar 🕅 Limpar                                              | Resistência            | 1.2k               | A         |

| A Enviar 🛍 Limpar                                              | Previous               | 1 2 3 4            | 4 5       |

#### **5. Development – Max Lists**

| *Instrument card                    | *CompBoard6           |

|-------------------------------------|-----------------------|

| VFGENA_FGENA1 A 0 max:5             | R_R10 A B 100         |

| VDC+6V_3 A vmax:6 imax:0.5          | BLACKBOX4_1 0 C D A 1 |

| VDC+25V_24_4:1_7 E vmax:10 imax:0.5 |                       |

| *CompBoard1                         | *CompBoard5           |

| compositur                          | L_L1 A B 680u         |

| R_R11 C 0 4.7k                      | C_C3 B C 100n         |

| SHORTCUT_1_2 D E                    |                       |

| *Course Doorsel4                    | R_R3 B C 180          |

| *CompBoard4                         | R_R4 B C 100          |

| R R1 A B 470                        | R_R5 B C 27           |

| R_R2 C D 470                        | R_R6 C D 10k          |

|                                     | R_R7 C D 4.7k         |

| D_D1 A B 1N4148                     | R_R8 C D 1k           |

| D_D2 C D 1N4148                     | R_R9 A B 1k           |

| C_C1 B C 220u                       |                       |

|                                     |                       |

|                                     |                       |

#### SHORTCUT\_1 B C

SHORTCUT\_2 D 0 SHORTCUT\_3 C D SHORTCUT\_4 B 0 SHORTCUT\_5 C 0

#### **5. Development – Maxlist Editor**

| VISIR                                                          |                                                                                                                                                                                                     | Menu +                                                             |

|----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| < Voltar                                                       |                                                                                                                                                                                                     |                                                                    |

|                                                                | Circuit_P.max                                                                                                                                                                                       |                                                                    |

|                                                                | VDCCOM_10<br>VDC+6V_1A<br>R_4_1G16.8k<br>R_4_2 C D 6.8k<br>SHORTCUT_1_5 F 0<br>SHORTCUT_1_61G<br>SHORTCUT_1_131E<br>SHORTCUT_2_11A C<br>SHORTCUT_3_14 D E<br>SHORTCUT_3_12 C G<br>SHORTCUT_3_14 E F |                                                                    |

|                                                                |                                                                                                                                                                                                     |                                                                    |

|                                                                | Tenviar CRedefinir                                                                                                                                                                                  |                                                                    |

|                                                                | Home · Experiências · Professor ·Administrador · Contato · VISIR                                                                                                                                    |                                                                    |

| "This project has been funded with support from the European C | commission. This website reflects the views only of the author, and the Commission cannot be held responsible f<br>VISIR+ © 2017                                                                    | or any use which may be made of the information contained therein" |

#### **5. Development – Maxlist Management**

| Max Lists                 |              |                      | <b>₽ 0</b> |

|---------------------------|--------------|----------------------|------------|

| Circuit P.max             | ۲.<br>۲      | Circuit_S.max        | ۲.<br>۲.   |

| EXP_1.max                 | ي م<br>الا 🗶 | Exp_2.max            | ی ک<br>۲ ک |

| TA_circuit_1.max          | ĭ ×          | TA_circuit_2_RCL.max | ⊡ ×        |

| TA_circuit_2_RLC.max      | <b>Z</b> ×   | TA_circuit_3_a.max   | <b>3</b> × |

| TA_circuit_3_b.max        | I 🗙          | TA_circuit_4.max     | 🕑 🗙        |

| TA_circuit_5.max          | <b>3</b> ×   | TA_demo1.max         | 🕑 🗙        |

| TA_demo2.max              | <b>Z</b> ×   | cap_ind_RLCserie.max | <b>3</b> × |

| circ_1_mvb.max            | <b>Z</b> ×   | circ_2_mvb.max       | <b>3</b> × |

| circ_3_mvb.max            | <b>Z</b> ×   | circ_4_mvb.max       | 🕑 🗙        |

| diodo_1_funcionamento.max | I 🗹 🗙        |                      |            |

#### Home · Experiências · Professor ·Administrador · Contato · VISIR

"This project has been funded with support from the European Commission. This website reflects the views only of the author, and the Commission cannot be held responsible for any use which may be made of the information contained therein"

VISIR+ © 2017

#### **5. Development - Contact**

| VISIR |                                                         | Menu + |

|-------|---------------------------------------------------------|--------|

|       | Formulário de Contato                                   |        |

|       | Nome:                                                   |        |

|       | E-mail:                                                 |        |

|       | Mensagem:                                               |        |

|       |                                                         |        |

|       | Destinatário:<br>Escolher                               |        |

|       | 🖈 Enviar 🛍 Limpar                                       |        |

| Hom   | e · Experiências · Professor ·Administrador · Contato · | VISIR  |

This project has been funded with support from the European Commission. This website reflects the views only of the author and the Commission cannot be held responsible for any use which may be made of the information contained th

VISIR+ © 2017

Co-funded by the Erasmus+ Programme of the European Union

# Thank you for your attendance!

Speaker André Fidalgo ISEP/IPP